公取委、飲食店情報サイトを調査=「不当な押し付け」などの有無確認:時事ドットコム https://www.jiji.com/sp/article?k=2019100900837&g=eco

公取委、飲食店情報サイトを調査=「不当な押し付け」などの有無確認:時事ドットコム https://www.jiji.com/sp/article?k=2019100900837&g=eco

Gentoo の emerge @preserved-rebuild が 2 つだけなのに終わらんなとおもってよく見たら LLVM をビルドしてた。終わらんわ。

もしかして experimental flag を気がつかずに入れていたとかの案件で mainline だと結局入ってない気がしてきた

Project:Kernel/Experimental - Gentoo Wiki

https://wiki.gentoo.org/wiki/Project:Kernel/Experimental#Additional_CPU_optimizations_for_GCC

今年の春に似たようなパッチが送られたときはまたいつものやつかという感じに一蹴されてた https://lkml.org/lkml/2019/2/21/1011

もしかして gentoo-sources の experimental フラグ有効にすると当てられてたあのパッチか!?

Welcome to Gentoo is Rice, the Volume goes to 11 here. - https://www.shlomifish.org/humour/by-others/funroll-loops/Gentoo-is-Rice.html

LKML: Alexey Dobriyan: Linux 5.0-ad1: -march=native support - https://lkml.org/lkml/2019/3/4/698

べつに Kconfig 改造していままでも付けたりはできただろうけどそれをして SSE とかそゆの使った結果まともに動かなくなりましたじゃ話にならんし追加に慎重になる必要があったのでは。まあ LKML で対象の patch mail をちゃんと見ればそこの経緯はわかるはずだけどまだ見てない

このアカウントは、notestockで公開設定になっていません。

の投稿

2bo@mstdn.maud.io

の投稿

2bo@mstdn.maud.ioこのアカウントは、notestockで公開設定になっていません。

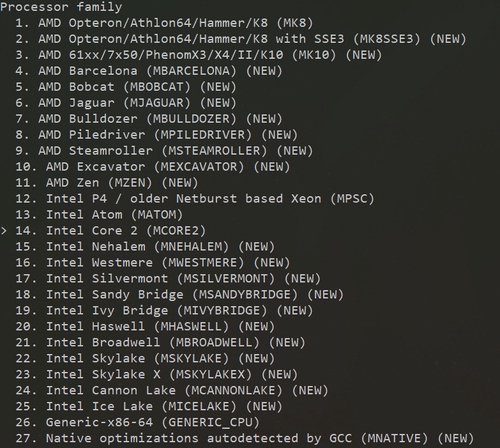

これ CPU family 覚えてなくてもとりあえず一番下のを選んでおけばいちばん速いオプションつけてくれるから安心。クロスビルドのときだけ他のをえらべばいいかな

New って書いてないやつしか元々なかったから,このオプション変えるだけでもわりと目に見えて速くなる環境ありそう。(しかしこれ Skylake とかでビルドすると AVX をカーネル内で使うとかも可能性あるのかな

Linux kernel のビルドのときの最適化オプションがいつのまにかたくさん増えてた(ちょっと前まで Core 2 とかしか選べなかったのに

このアカウントは、notestockで公開設定になっていません。

ちなみに最初のIEEE 1364-1995は"IEEE Standard Hardware Description Language Based on the Verilog(R) Hardware Description Language"だった

Verilogは元々シミュレーターの名前なので、HDLだけを明確に指したいときにはVerilog HDLと書く(IEEE 1364-2005のタイトルも"IEEE Standard for Verilog Hardware Description Language")

そういえば x86 は実は Intel SDM が本当によく書けてるおかげで他のプロセッサ以上にマニュアル読めばなんでもわかるおかげでラクなところがあるというハナシがあります

FPGA ボード用のピンヘッダ作って CPU もどきつくる復習でもやるかおもってたけどピンヘッダ作るのが面倒で放置してたし今度秋葉原行ったらピン買うか

Aarch64 や MIPS64 もまあ既存のコード読めば理解できると思うけどなにせ Linux とかの既存のものは essential な部分以外の config や機能での分岐が多くて敵わん

まあ x86 は面倒なとこもあるけどその代わり xv6 という優秀なテクストとコードがあるからこれ一通り読めばあらかた OS に必要なとこは理解できるし

それと x64 と Aarch64 ぐらいは多少はそこらへん把握してないとそもそも OS 論文読むの困難なんだよな

このアカウントは、notestockで公開設定になっていません。

このアカウントは、notestockで公開設定になっていません。

このアカウントは、notestockで公開設定になっていません。

x86 以外は OS 作れるほどよく知らないのなんとかしたい思ってたしなんか OS の arch 読むかでも Linux はしんどいーって考えてたので丁度いいな。Arm 読むかーとか以前考えてたけど RISC-V のほうがアツいし

xv6のRISC-V版を作って6.828的な講義をやるかもしれないという噂は何年か前から聞こえていて、とうとう今年からそうなるという話になった

おっ,MIT の 6.828 で使われてた xv6 が新しいコース 6.S081 向けに RISC-V に移植されてるっぽい! >> 6.S081 / Fall 2019 https://pdos.csail.mit.edu/6.828/2019/xv6.html

UT は OS はないけど x64 で multiboot で起動するまでのコードは与えられて,あとは割り込み禁止してページテーブル作って割り込みハンドラ書いて……みたいなベアメタルプログラミングは演習があったはず

ほかのとこでも CPU とコンパイラやるとこはそこそこある(CPU は ISA 用意されてて設計も手順をインクリメンタルに教えていくものから,ALU を作るまでで終わるとこまで)。ただ完全にイチから手前でやれ(あとは放置)みたいなのは東大理情だけじゃないかね

ただ理情の CPU 実験はコンパイラはほぼほぼ OCaml サブセットな(たしか住井先生の)教育言語のが用意されてるからあんまやることないはずで,CPU のほうは ISA 設計からやるしんどいやつだけど 3 人ぐらいで班組んでやるからあんま FPGA 触らない分担の人が出ることもある。まあそれでも重い内容だけど

このアカウントは、notestockで公開設定になっていません。

このアカウントは、notestockで公開設定になっていません。

このアカウントは、notestockで公開設定になっていません。

ところでこれみて >> AUR (en) - sprout-git https://aur.archlinux.org/packages/sprout-git/